# AN993 APPLICATION NOTE

# ELECTRONIC BALLAST WITH PFC USING L6574 AND L6561

The advent of dedicate IC for lamp ballast applications is replacing the old solutions based on bipolar transistor driven by a saturable pulse transformer.

The L6574 is a high performance ballast driver, designed in 600V BCD OFF-LINE technology, which ensures all the features needed to drive and control properly a fluorescent bulb. It is provided with a built-in VCO start up sequence circuitry, Protections, and an OP-AMP, useful to implement a closed loop control of the lamp current.

#### 1 INTRODUCTION

# 1.1 Half bridge converter for electronic lamp ballast

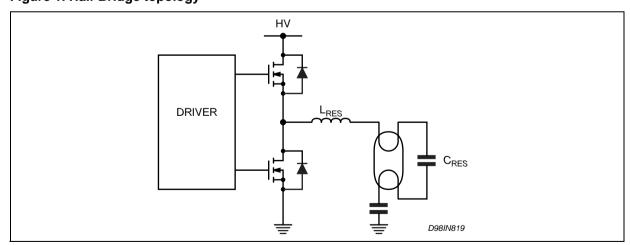

Voltage fed series resonant half bridge inverters are currently used for fluorescent lamps (fig.1). This topology allows to easily operate in Zero Voltage Switching (ZVS) resonant mode, drammatically reducing the transistor switching losses and the electromagnetic interference.

To design a cost effective, compact and smart electronic lamp ballast it could be used a dedicated IC able to drive directly the power MOSFETs of the half bridge. Such controllers require a high voltage capability for the high side floating transistor driver.

Figure 1. Half Bridge topology

# 1.2 Lamp requirements

To provide long life and to insure an efficient ignition of the lamp the cathodes must be preheated. In fact the preheating of the filaments allows an easy strike of the lamp reducing ignition voltage. During preheating time the lamp is characterised by a high impedance and the current flows only in the filaments. The resistance value

May 2004 1/20

of the filaments are strictly dependent on the lamp model. Typically these filaments present a initial low value (a few Ohms) that will increase by 4-5 times during the preheating.

After the preheating time the lamp must be ignited, by increasing the voltage across it. The ignition voltage value also depends on the lamp type, and it increases with the aging. For a typical TL 58W it is not much less than 1000V. Using a simple inverter, with a constant switching frequency, external circuitry must be used (e.g. PTC or discrete timer). Instead with the ST L6574 smart controller both the preheating and the ignition functions are achieved by using simple resistors and a capacitor, which set all the start-up procedure.

#### 2 L6574 BALLAST DRIVER

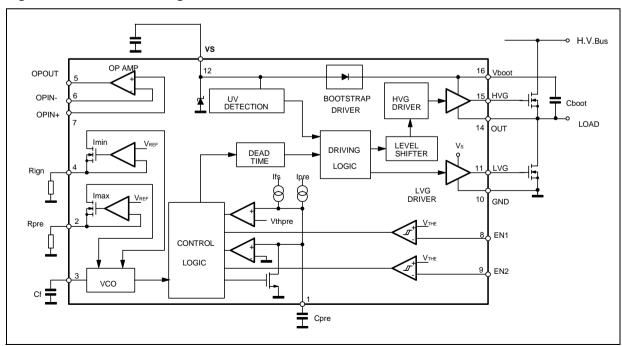

The L6574, whose internal block diagram is shown in fig.2, is an IC intended to drive two power MOS or IGBT in half bridge topology, ensuring all the features needed to drive and control properly a fluorescent bulb. Moreover, by varying the switching frequency it is possible to modulate the current in the lamp, therefore the output power. The device is available in DIP16 and SO16N packages.

The most significant features of the L6574 concern the following points:

- high voltage rail up to 600V;

- dV/dt immunity ± 50 V/ns in full temperature range;

- driver current capability (250 mA source and 450 mA sink);

- switching times 80/40 ns rise fall with 1 nF load;

- CMOS shut down input;

- under voltage lock out;

- preheat and frequency shifting timing;

- sense OP AMP for closed loop control or protection features;

- high accuracy current controlled oscillator;

- integrated bootstrap diode;

- clamping on V<sub>S</sub>;

- SO16, DIP16 package

Figure 2. Internal Block diagram of the L6574

+ HVBus -||-**I**D1 CSnub CSupply **★** D2 Qh 16 15 R1 L\_ballast 14 QI Rpre. 11 L6574 R5 | 8 Cres LAMP R6 **★** D3 D4 10 Ref. R2 СЗ Cpre R4 R9 C1 = ∐<sub>Rign.</sub> **‡**Cf R7 Rcs R3 C4 R8

Figure 3. Typical Application's Connection

**Table 1. Device Pins Description**

| N. | Name | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | CPRE | Preheat Timing Capacitor. The capacitor $C_{PRE}$ sets the preheating and the frequency shift time, according to the relations: $t_{PRE} = K_{PRE} \cdot C_{PRE}$ and $t_{SH} = K_{FS} \cdot C_{PRE}$ (typ. $K_{PRE} = 1.5$ s/ $\mu$ F, $K_{FS} = 0.15$ s/ $\mu$ F). This feature is obtained by charging CPRE with two different currents. During tPRE this current is independent of the external components, so CPRE is charged up to 3.5V (preheat timing comparator threshold). During $t_{SH}$ the current depends on $t_{RRE}$ value (i.e. on the difference between $t_{RRE}$ and $t_{IGN}$ ). In this way $t_{SH}$ is always set at 0.1 $t_{RRE}$ . In steady state the voltage at pin 1 is 5V (see fig.5). |

| 2  | RPRE | Maximum Oscillation Frequency Setting. The resistance connected between this pin and ground sets the fPRE value, fixing the difference between $f_{PRE}$ and $f_{IGN}$ ( $f_{PRE} > f_{IGN}$ ). At the end of the Start-up procedure, the effect current drown from $R_{PRE}$ is over. The voltage at this pin is fixed at $V_{REF} = 2V$ .                                                                                                                                                                                                                                                                                                                                                                          |

| 3  | CF   | Oscillator Frequency Setting. The capacitor $C_F$ , along with to $R_{PRE}$ and $R_{IGN}$ , sets $f_{PRE}$ and $f_{ING}$ . In normal operation this pin shows a triangular wave.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4  | RIGN | Minimum Oscillation Frequency Setting. The resistance connected between this pin and ground sets the $f_{\text{IGN}}$ value. The voltage at this pin is fixed at $V_{\text{REF}}$ =2V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

**Table 1. Device Pins Description (continued)**

| N. | Name  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 5  | OPout | Out of the operational amplifier. To implement a feedback control loop this pin can be connected to the RIGN pin by means an appropriate circuitry.                                                                                                                                                                                                                                                                                                                    |  |

| 6  | OPin- | Inverting Input of the operational amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 7  | OPin+ | Non Inverting Input of the operational amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 8  | EN1   | Enable 1. This pin (active high), forces the device in a latched shutdown state (like in the under voltage conditions). There are two ways to resume normal operation:  - the first is to reduce the supply voltage below the undervoltage threshold and then increase it again until the valid supply is recognised.  - the second is activating EN2 input (see fig. 10).  The enable 1 is especially designed for strong fault (e.g. in case of lamp disconnection). |  |

| 9  | EN2   | Enable 2. EN2 input (active high) restarts the start-up procedure (preheating and ignition sequence). This features is useful if the lamp does not turn-on after the first ignition sequence (see fig. 9).                                                                                                                                                                                                                                                             |  |

| 10 | GND   | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 11 | LVG   | Low Side Driver Output. This pin must be connected to the low side power MOSFET gate of the half bridge. A resistor connected between this pin and the power MOS gate can be used to reduce the peak current.                                                                                                                                                                                                                                                          |  |

| 12 | VS    | Supply Voltage. This pin, connected to the supply filter capacitor, is internally clamped (15.6V typical).                                                                                                                                                                                                                                                                                                                                                             |  |

| 13 | N.C.  | Non Connected. This pin set a distance between the pins related to the HV and those related to the LV side.                                                                                                                                                                                                                                                                                                                                                            |  |

| 14 | OUT   | High Side Driver Floating Reference. This pin must be connected close to the source of the high side power MOS or IGBT.                                                                                                                                                                                                                                                                                                                                                |  |

| 15 | HVG   | High Side Driver Output. This pin must be connected to the high side power MOSFET gate of the half bridge. A resistor connected between this pin and the power MOS gate can be used to reduce the peak current.                                                                                                                                                                                                                                                        |  |

| 16 | VBOOT | Bootstrapped Supply Voltage. Between this pin and VS must be connected the bootstrap capacitor. A patented integrated circuitry replaces the external bootstrap diode, by means of a high voltage DMOS, synchronously driven with the low side power MOSFET.                                                                                                                                                                                                           |  |

# 3 DEVICE BLOCK DESCRIPTION

The preheating control section and the bootstrap section are tightly connected to application design. Here below there are some details on their working and how they have to be used.

# 3.1 Preheating and ignition section

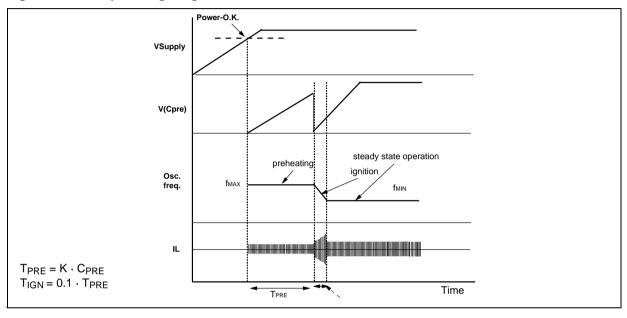

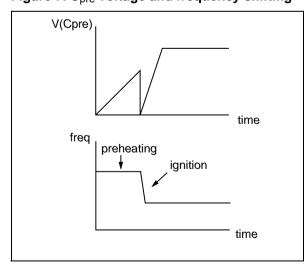

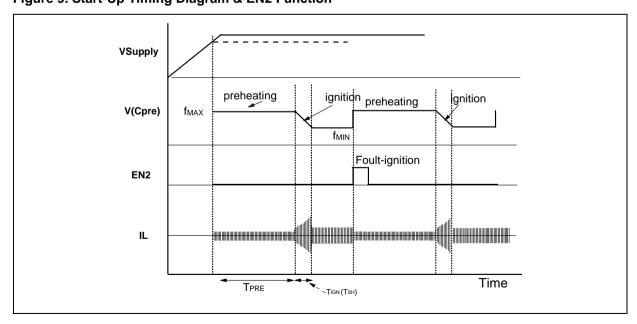

L6574 turn on sequence is divided into three phases: preheating, ignition and normal operation (fig. 4). Preheating phase is characterised by the highest oscillation frequency ( $f_{max}$ ) for a period  $T_{pre}$ . During ignition phase the frequency shifts from  $f_{max}$  to  $f_{min}$  (that is the normal operation frequency) in a period  $T_{sh}$ .

Figure 4. Start-Up Timing Diagram & EN2 Function

All the parameters specified above are set choosing properly few external components.

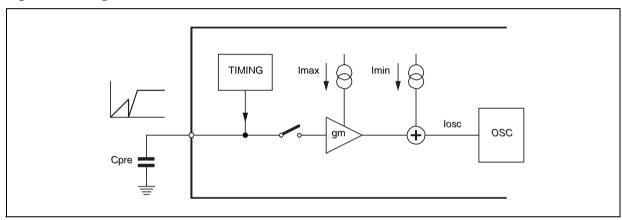

T<sub>pre</sub> and T<sub>sh</sub> are set by means of the capacitor C<sub>pre</sub> that is connected at pin 1.

During the preheating time,  $T_{pre}$ , the capacitor Cpre is charged by means of a constant current  $I_{pre}$  internally generated, which doesn't depend on the external components. The voltage across  $C_{pre}$  increases linearly up to the "preheating threshold", in which the preheating phase finishes.

$$T_{pre} = C_{pre} \cdot \frac{V_{th}}{I_{pre}}$$

, where  $V_{th}$  = 3.5V and  $I_{pre}$  = 2.3 $\mu$ A

That is to say:

$$T_{pre} = 1.5 \text{s}/\mu\text{F} \cdot \text{C}_{pre}$$

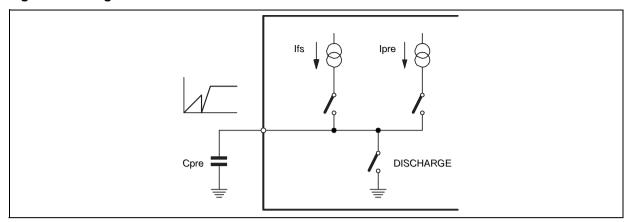

Figure 5. Timing block

Figure 6. Timing Oscillator block

After the preheating time the capacitor  $C_{pre}$  is first quickly discharged, and then recharged by the current Ifs, generating a second voltage ramp which fed a transconductance amplifier, as shown in fig. 6 (the switch is closed). Thus this voltage signal is converted in a growing current which is subtracted to Imax, to produce the frequency shifting from  $f_{max}$  to  $f_{min}$ . The current which drives the oscillator to set the frequency during the shifting is equal to:

$$I_{osc} = I_{min} + (I_{max} - g_m V_{Cpre}(t - T_{pre})) = I_{min} + \left(I_{max} - \frac{g_m I_{fs}}{C_{pre}}(t - T_{pre})\right)$$

[a]

Where:

$$I_{min} = \frac{V_{REF}}{R_{ign}}, I_{max} = \frac{V_{REF}}{R_{pre}}, V_{REF} = 2V$$

Rign and Rpre are the resistors connected to pin 4 and pin 2.

At the end of preheating time ( $t = T_{pre}$ ) L6574 oscillates at fmax, set by:

$$I_{osc}(T_{pre}) = I_{osc}0) = I_{min} = I_{max} = V_{REF}\left(\frac{1}{R_{ign}} + \frac{1}{R_{pre}}\right)$$

That means that the preheating frequency depends on both Rpre and Rign.

At the end of the frequency shifting (t = Tpre + Tsh), the second term of eq.[a] decreases to zero and the switching frequency is set only by Imin (i.e. Rign):

$$I_{osc}(T_{sh}) = I_{min} = \frac{V_{REF}}{R_{ign}}$$

Since the second term of eq. [a] is equal to zero, we have:

$$I_{max} - \frac{g_m I_{fs}}{C_{pre}} T_{sh} = 0 \rightarrow T_{sh} = \frac{C_{pre} I_{max}}{g_m I_{fs}} [b]$$

Note that there is not a fixed threshold of the voltage across Cpre in which the ignition phase finishes (i.e. the end of the frequency shifting):  $T_{sh}$  depends on  $C_{pre}$ ,  $I_{max}$ ,  $g_m$ , and  $I_{fs}$  (eq. [b]). This fact can be seen also in fig. 7. Making  $T_{sh}$  independent of  $I_{max}$ , the  $I_{fs}$  current has been designed to be a fraction of  $I_{max}$ , so:

$$I_{fs} = \frac{I_{max}}{K} \rightarrow T_{sh} = \frac{C_{pre}I_{max}}{g_{m}I_{max}K} \rightarrow T_{sh} = \frac{C_{pre}}{g_{m}K} \rightarrow T_{sh} = k_{fs}C_{pre}$$

In this way the frequency shift time depends only by the capacitor  $C_{pre}$ . The typical value of the  $k_{fs}$  constant (Frequency Shift Timing Constant) is 0.15 s/ $\mu$ F, that is:

$$k_{fs} = k_{pre}/10$$

.

So choosing Cpre both  $T_{pre}$  and  $T_{sh}$  are set.

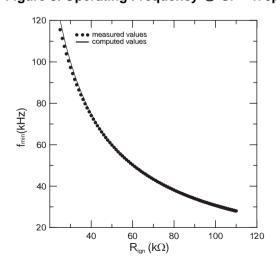

The frequencies  $f_{min}$  and  $f_{max}$  depend on the resistors  $R_{pre}$  and  $R_{ign}$ , but also on the capacitor  $C_f$  (Oscillator frequency setting -> capacitor at pin 3).  $f_{min}$  is set choosing  $C_f$  and  $R_{ign}$ , then with  $R_{pre}$  the  $\Delta f = f_{max}$  -  $f_{min}$  is set. Simplified equations can be used:

$$f_{min} = \frac{1.41}{R_{ign} \cdot C_f}$$

$$f_{max} = \frac{1.41 \cdot (R_{pre} + R_{ign})}{R_{pre} \cdot R_{ign} \cdot C_f}$$

These equation fit well with measured values, especially in the frequencies range 30 to 100kHz: in fig. 8 there is a comparison between fmin measured and computed data (@ C<sub>f</sub> = 470pF).

Figure 7. Cpre voltage and frequency shifting

Figure 8. Operating Frequency @ Cf = 470pF

To summarise:

Table 2.

| parameter                                    | set choosing                      |

|----------------------------------------------|-----------------------------------|

| T <sub>pre</sub>                             | C <sub>pre</sub>                  |

| T <sub>sh</sub>                              | C <sub>pre</sub>                  |

| $\Delta f = f_{\text{max}} - f_{\text{min}}$ | R <sub>pre</sub>                  |

| f <sub>min</sub>                             | R <sub>ign</sub> & C <sub>f</sub> |

If  $R_{pre}$  is not connected at pin 2, there is no  $\Delta f$ , so  $f_{max}$  and  $f_{min}$  have the same value. Moreover there is no  $I_{max}$ , that is to say there is no  $I_{fs}$ . In this case  $C_{pre}$  is charged only once by  $I_{pre} = 2.3 \mu A$  up to 3.5V (fig 8: there is only the first voltage raising) . When  $C_{pre}$  is discharged there is no current  $I_{fs}$  to charge it once more. If  $R_{pre}$  has been connected when preheating and ignition phases are ended, pin  $I(C_{pre})$  is at 4.8-5V with a current capability of few  $I_{rad}A$  (1/6  $I_{rad}A$ ). If  $I_{rad}A$  is not connected,  $I_{rad}A$  is at GND level in normal operation phase.

#### 3.2 Controls section.

L6474 is provided with two control's functions, EN1 and EN2. Both the functions are active high. To well understand the effect of this functions, please refer to figures Fig. 9 and Fig. 10.

- EN1 (latched enable) is dedicated to stop all the functions of the device and it is usually activated in case of strong fault (i.e. lamp disconnection). It is possible to cancel this status, in two different way: reducing the supply voltage below its minimum threshold or activating the second control pin EN2 (EN2 overrides EN1). As the device start again restarts to operate, the start-up sequence will be reactivated.

- EN2 (Repeating start-up) is dedicated to restart the preheating and ignition procedure; it is normally activated when the application fails to ignite the lamp. As the EN2 is activated the starting procedure restarts. To be considered that the L6574 operates to the maximum frequency for all the time that EN2 is active.

Figure 9. Start-Up Timing Diagram & EN2 Function

LVG

HVG

Latched enable

EN1

EN2

Forced restart

Time

Figure 10. Controls Timing Diagram

# 3.3 Bootstrap section

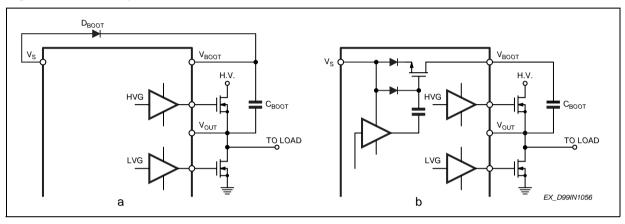

A bootstrap circuitry is needed to supply the high voltage section. This function is normally accomplished by a high voltage fast recovery diode (fig. 11a). In the L6574 a patented integrated structure replaces the external diode. It is realised by a high voltage DMOS, driven synchronously with the low side driver (LVG), with in series a diode, as shown in fig. 11b

An internal charge pump (fig. b) provides the DMOS driving voltage .

The diode connected in series to the DMOS has been added to avoid undesirable turn on of it.

C<sub>boot</sub> selection and charging:

To choose the proper  $C_{boot}$  value the external MOS can be seen as an equivalent capacitor. This capacitor  $C_{ext}$  is related to the MOS total gate charge :

$$C_{ext} = \frac{Q_{gate}}{V_{gate}}$$

The ratio between the capacitors Cext and Cboot is proportional to the cyclical voltage loss. It has to be:

e.g.: if  $Q_{gate}$  is 30nC and  $V_{gate}$  is 10V,  $C_{ext}$  is 3nF. With  $C_{boot} = 100$ nF the drop would be 300mV.

If HVG has to be supplied for a long time, the C<sub>boot</sub> selection has to take into account also the leakage losses.

The internal bootstrap driver gives great advantages: the external fast recovery diode can be avoided (it usually has great leakage current). This structure can work only if  $V_{out}$  is close to GND (or lower) and in the meanwhile the LVG is on. The charging time ( $T_{charge}$ ) of the  $C_{boot}$  is the time in which both conditions are fulfilled and it has to be long enough to charge the capacitor.

The bootstrap driver introduces a voltage drop due to the DMOS R<sub>dson</sub> (typical value @25° is 150 Ohm). At low frequency this drop can be neglected. Anyway increasing the frequency it must be taken in to account.

The following equation is useful to compute the drop on the bootstrap DMOS:

$$V_{drop} = I_{charge}R_{dson} \rightarrow V_{drop} = \frac{Q_{gate}}{T_{charge}}R_{dson}$$

where  $Q_{gate}$  is the gate charge of the external power MOS,  $R_{dson}$  is the on resistance of the bootstrap DMOS, and  $T_{charge}$  is the charging time of the bootstrap capacitor.

For example: using a power MOS with a total gate charge of 30nC the drop on the bootstrap DMOS is about 1V, if the  $T_{charge}$  is  $5 \mu s$ . In fact:

$$V_{drop} = \frac{30nC}{5\mu s} \cdot 150\Omega \sim 0.9V$$

V<sub>drop</sub> has to be taken into account when the voltage drop on C<sub>boot</sub> is calculated: if this drop is too high, or there is not a sufficient charging time, an external diode can be used.

Figure 11. Bootstrap driver

# 4 DEMO APPLICATION DESCRIPTION

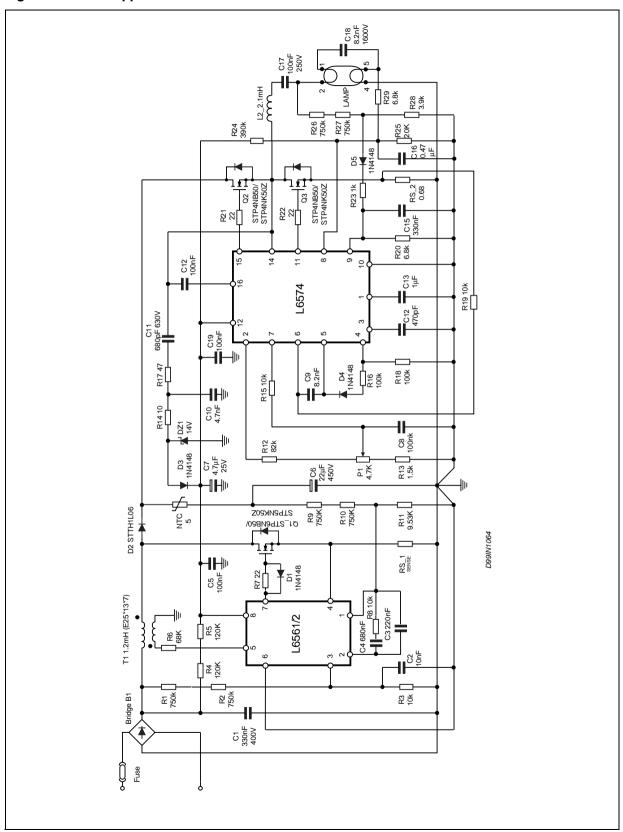

The design has been developed to drive a TL fluorescent lamp up to 58W. It is composed of two sections: the PFC, using the L6561 controller, and the ballast, based on the L6574 (see fig.9 and fig.10). The application is provided with a current feedback, that allows power control (and in case the dimming function) by varying the switching frequency during the normal lamp burning. The application is also provided with a safety circuitry, that acts in case of open load or faulty ignition of the lamp.

**A**7/

Figure 12. Demo Application circuit

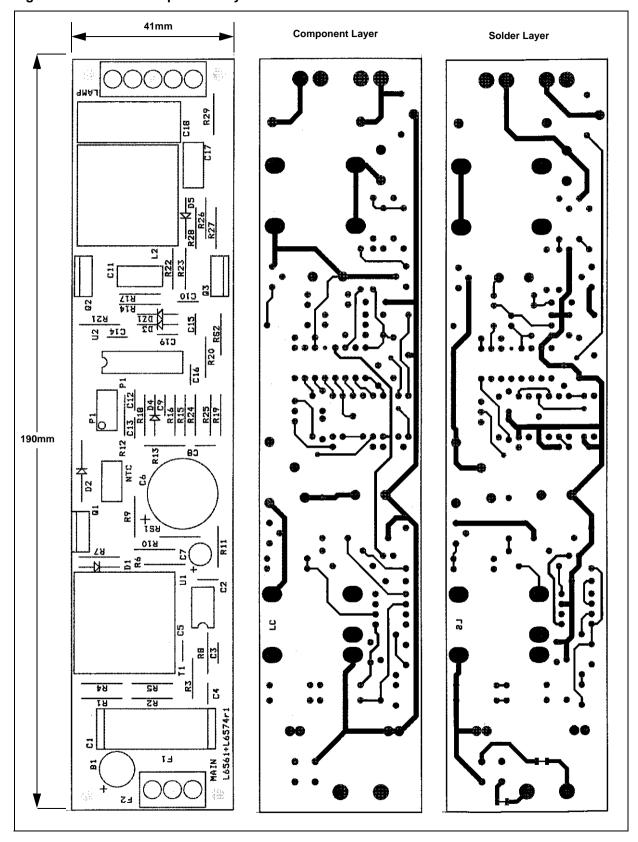

Figure 13. PCB and components layout.

# 4.1 Power factor section

Even if the PFC stage is not strictly necessary for electronic ballast application, in this design it has been introduced for the following reasons.

The front-end stage of conventional off-line converters, typically made up of a full wave rectifier bridge with a capacitor filter, gets an unregulated DC bus from the AC mains. Therefore the instantaneous line voltage is below the voltage on the capacitor most of the time, thus the rectifiers conduct only for a small portion of each line half-cycle. The current drawn from the mains is then a series of narrow pulses whose amplitude is 5-10 times higher than the resulting DC value.

Lots of drawbacks result from that: much higher peak and RMS current drawn from the line, distortion of the AC line voltage, overcurrents in the neutral line of the three-phase systems and, after all, a poor utilisation of the power system's energy capability.

This can be measured in terms of either Total Harmonic Distortion (THD), as norms provides for, or Power Factor (PF), intended as the ratio between the real power (the one transferred to the output) and the apparent power (RMS line voltage times RMS line current) drawn from the mains, which is more immediate. A traditional input stage with capacitive filter has a low PF (0.5-0.7) and a high THD (> 100%).

The new European norms and the International standard requirements have spurred the design of high power factor ballasts and they are starting to impose a limit on the input current harmonic content. For these reasons power factor corrector (PFC) is now diffusing in consumer and industrial lighting. With a high power factor switching preregulator, interposed between the input rectifier bridge and the bulk filter capacitor, the power factor will be improved (up to 0.99). The current capability is increased, the bulk capacitor peak current and the harmonic disturbances are reduced.

The L6561/2 is an IC intended to control PFC preregulators by using the transition mode technique and is optimised for lamp ballast applications.

The operation can be summarised in the following description (for more information, see AN966). The AC mains voltage, that can range from 85V to 265V, is rectified by a diodes bridge and delivered to the boost converter. The boost converter consists of a boost inductor  $(T_1)$ , a controlled power switch  $(Q_1)$ , a catch diode  $(D_2)$ , an output capacitor  $(C_6)$  and, obviously, a control circuitry (see fig.3).

The PFC section has been designed to supply a 400V DC and a power of 60W.

#### 4.2 Ballast Section

The regulated voltage is delivered to the ballast section. The ballast is based on the high performances L6574, which is an OFF-LINE half bridge driver designed in 600V BCD technology. It adds to the full integrated half bridge driver topology a built-in voltage controlled oscillator (VCO), a preheating start-up procedure and an operational amplifier dedicated to the feedback loop. To avoid cross conduction of the power MOSFETs or IGBTs, the internal logic ensures a minimum dead time.

The load consists of a series resonant circuit ( $L_2$ - $C_{18}$ ) with the lamp connected across the capacitor ( $C_{18}$ ). This topology allows to operate in Zero Voltage Switching, to reduce the transistor switching losses and the electromagnetic interference generated by the output wiring of the lamp.

The blocking capacitor (C<sub>17</sub>) allows to obtain a zero average lamp current. In steady state the voltage across these capacitors is as high as half the high voltage bus, that is about 200V.

#### 4.3 Preheating and ignition sequence

The turn-on sequence can be divided in three phases: preheating, ignition and normal lamp burning. The preheating of the lamp filaments is achieved by a high switching frequency  $f_{PRE}$ , about 60 kHz, set by  $R_{PRE} = R_{12} + P_1 + R_{13}$  and  $C_F = C_{12}$ , to ensure that a current flows in the filaments without lamp ignition. In fact the initial voltage applied across the lamp is below the strike potential. The duration of the preheating period  $T_{PRE}$  is set by the capacitor  $C_{PRE} = C_{13}$ . The choice of this time is strictly dependent on the lamp type. In the application  $T_{PRE}$  has been set at 1.5 sec.

The ignition sequence begins after  $T_{PRE}$ . The switching frequency decreases towards the resonance point ( $L_2$ - $C_{18}$ ), increasing the voltage across the lamp, and causing the ignition. The time interval in which the frequency shifts,  $t_{SH}$ , amounts to  $t_{SH} = t_{PRE}/10 = 150$ ms. At the end of tSH the frequency reaches 31 kHz ( $R_{18}$ - $C_{12}$ ), and then the current feedback loop is activated.

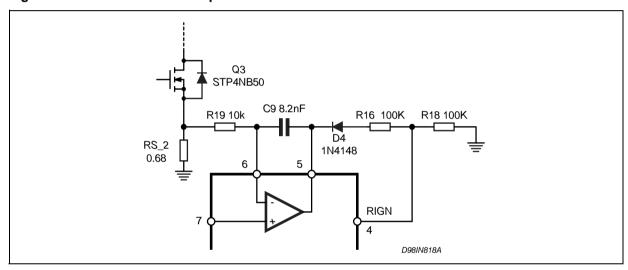

# 4.4 Current feedback loop

The current control is achieved by varying the switching frequency of the VCO. Since controlling the average current in the lamp means controlling the output power, it is quite easy to perform control function. The OP-AMP compares the low-pass filtered half-bridge current with a reference, achieved by a portion of the voltage at pin 2 ( $V_{PIN2} = 2V$ ). This set-point could be changed by the trimmer  $P_1$ , to perform the dimming function. The OP-AMP output is connected to  $R_{ING}$  pin by  $D_4$  and  $R_{16}$ . The diode  $D_4$  is necessary to avoid that the switching frequency decreases below the value set by  $R_{18}$ .

At start-up the voltage across  $R_{S2}$  (fig.14) remains low until the lamp ignition. So the inverting input of OP-AMP (pin 6) stays low too, while the non inverting input (pin 7) is set at a constant voltage (set-point) by the divider  $R_{12}$ ,  $P_1$  and  $R_{13}$ .

Therefore the OP-AMP output (pin 5) remains high (5V) until the lamp ignition, and D<sub>4</sub> is off. In this condition the L6574 oscillates at f<sub>PRF</sub>.

As the lamp strikes on (after  $t_{PRE}$  and  $t_{SH}$ ), the average voltage across  $R_{S2}$  increases and the feedback is able to regulate the lamp current.

Figure 14. Current feedback loop

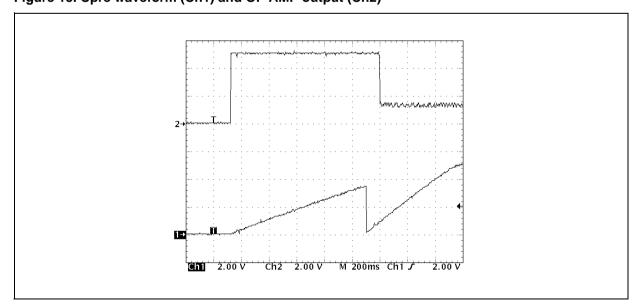

Figure 15. Cpre waveform (Ch1) and OP AMP output (Ch2)

# 4.5 Start-up and supply

The start-up procedure is very important in an application that contains two different sections.

The ballast section starts before the PFC, avoiding any extra-voltage at the PFC section output, and so the L6561 dynamic OVP activation (see AN966). This behaviour is guaranteed under all conditions because the VS turn-on threshold of L6574 is lower than the L6561/2 one.

At start-up the L6574 is powered by the resistor ( $R_4 + R_5$ ). This resistor must be chosen so as to ensure the "before start-up current" of both the L6561 and L6574.

When the ballast section is running, the charge pump ( $C_{11}$ ,  $R_{14}$ ,  $R_{17}$ ,  $D_3$  and  $D_{Z1}$ ) allows to supply both the devices. The resistor  $R_{17}$  and  $C_{10}$  allows to reduce the noise at  $V_{CC}$ .

# 4.6 Safety circuitry

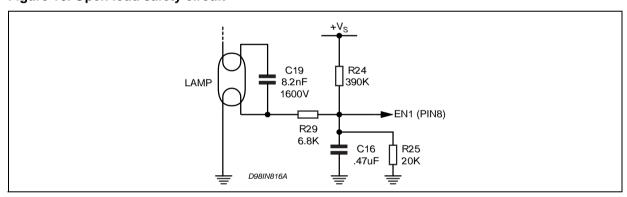

In normal operation the inductive load ensures a zero voltage switching mode, but if the lamp is disconnected the switching losses in the power MOSFETs will increase considerably. To prevent this occurrence a safety circuitry has been designed. When the lamp is connected the EN1 input (pin 8) of the L6574 is held close to ground by the series of  $R_{29}$ , the lamp filament and  $R_{S2}$ . If the lamp is not present EN1 is pulled up to  $V_S$  by  $R_{24}$ , forcing the L6574 in a latched shutdown state. To resume normal operation it is necessary to turn off the ballast and then turn it on again.

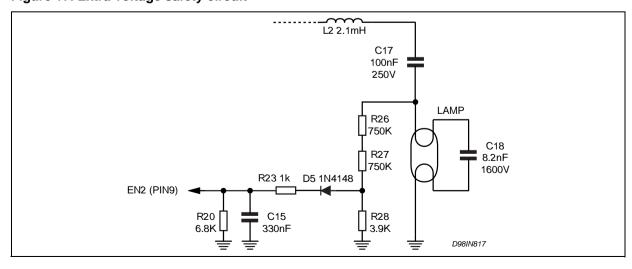

A second alarm has been designed to protect the application against the extra voltages which would arise if the lamp did not strike after the ignition sequence, because of an old lamp. A partition of this extra voltage is rectified and delivered to the EN2 input (pin 9) of the L6574, restarting the start-up procedure (preheat and ignition sequence).

Figure 16. Open load safety circuit

Figure 17. Extra voltage safety circuit

#### 5 DESIGN HINTS

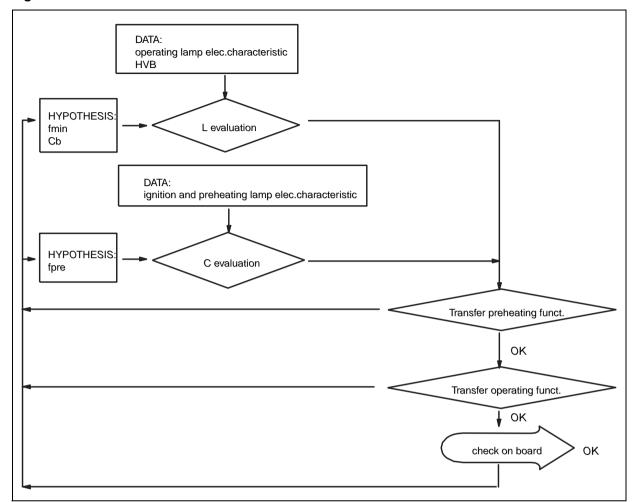

# 5.1 Inductance and capacitors evaluation

To design an application with L6574 a preliminary evaluation of the components can be done only fixing the lamp type and its electrical characteristics.

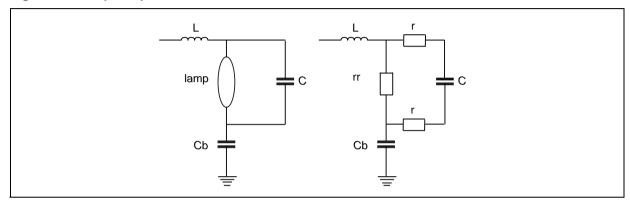

We can summarise this evaluation process in few marks, but this is an "iterative" process, because we have to do some assumptions that have to be checked at the end of the process. A simplified schematic can well represent the load:

Figure 18. Lamp Simplified Schematic

In fig. 18 r is the lamp filament resistance, rr is the operating lamp equivalent resistance ( when the lamp is off or during preheating rr is an open circuit).

First of all we have to evaluate a proper inductance value.

L has to give the right current value to the lamp when it is already ignited and is working ("choke" inductance). So it depends on the current required by the lamp , that is to say on the lamp operating wattage and voltage, on the operating frequency fmin, but also on the voltage across L and the lamp ( $V_b$ ). The greater  $V_b$  variation, the greater inductance in order to give a constant current to the lamp. Vb variations are due to the High Voltage Bus variations and to the ripple on half battery capacitor ( $C_b$ ). The ripple depends on  $C_b$  size, and we have to do a proper hypothesis on it to estimate  $V_b$  variation. Taking into account all these data and hypothesis, we can do some simplifying assumption: during operating condition the most of the current flows into the lamp, not into  $C_b$ , and all the power delivered to the system is delivered to the lamp.  $V_{lamp}$  is the operating voltage across the lamp and  $P_{lamp}$  is the operating lamp wattage, so a good approximation to conduct the choke inductance is:

$$L = \frac{V_L}{I_1 \cdot 2 \cdot \pi \cdot f} \rightarrow \frac{V_{lamp}}{P_{lamp}} \cdot \frac{(V_b - V_{lamp})}{2 \cdot \pi \cdot f_{min}}$$

The second step is the evaluation of the capacitance across the lamp (C).

When the lamp is not yet ignited, C has to allow a sufficient current to flow into the lamp filament in order to have a proper preheating. The power to be delivered to the lamp filaments (P<sub>fil</sub>), the preheating frequency, the lamp filament resistance r and the maximum voltage to be applied across C without causing lamp ignition are constraints that help to evaluate the capacitor size. Setting the current through the lamp filament and the max. voltage across the capacitor, you have a capacitor range of values.

$$C = I_C \cdot \frac{1}{2 \cdot \pi \cdot f \cdot V_C} \rightarrow \frac{\sqrt{Pfil}}{r} \cdot \frac{1}{2 \cdot \pi \cdot f_{pre} \cdot V_{Cmax}}$$

Those values of L, C<sub>b</sub> and C have to be corrected in order to have standard and commercial components values. Using these values and lamp equivalent resistances the transfer functions during preheating and operating condition can be calculate.

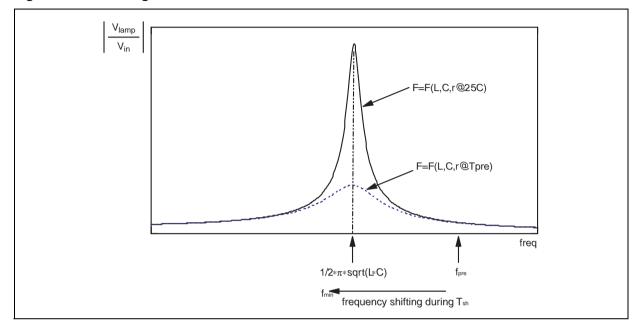

The preheating transfer function allows to see if moving towards the resonant frequency (L-C) there is a frequency at which the voltage across the lamp enables its ignition, and this frequency has to be between  $f_{max}$  and  $f_{min}$ . The transfer function gain depends also on r, but r changes greatly during preheating (also 3-4 times) and this has to be considered (see fig.19).

Figure 19. Preheating Transfer Function

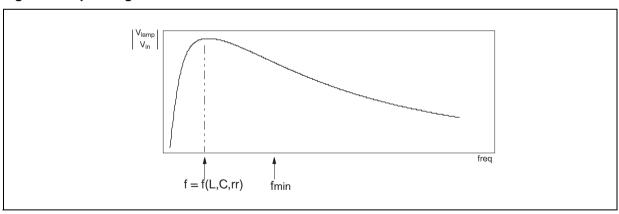

The operating transfer function allows to check if we have an operating voltage across the lamp (at  $f = f_{min}$ ) that is similar to the one used to evaluate L (fig. 20).

Figure 20. Operating Transfer Function

If one of these condition is not verified, the evaluation process has to be restarted changing the initial hypothesis: i.e. changing the frequencies, or the assumption on Cb ripple. If this everything is OK, the values found can be used, and a preliminary stage of design can be concluded: to better set the components and the frequencies values experiments are needed, also to verify the initial assumptions, and in case to reiterate another step of evaluation process with better assumptions.

The following flow chart can help the iteration process:

Figure 21. Iterative Process

# 6 HOW TO DIM THE LAMP

In the demo board the lamp is dimmed changing the working frequency.

The minimum working frequency is:

$$f_{min} = \frac{1.41}{R_{ign} \cdot C_f}$$

To change the working frequency we have to change the current that flows from pin 2. Using fig.9 circuit, the current that flows from pin n. 2 depends also on the op-amp out pin (pin n. 5) voltage: if V5>V2 for sure there will be no current in R16, and the frequency will be equal to fmin. Instead when the op amp out voltage gets lower the current that flows from pin 2 will go into R16 and R18: pin 2 sees the parallel between R18 and an equivalent resistor that depends on V5 and on D4 voltage:

$$R16_{equ} = \frac{V2 \cdot R16}{V2 - V_{diode4} - V5}$$

So the working frequency will be:

$$f_{work} = \frac{1.41}{(R_{ign} // R16_{equ}) \cdot C_f}$$

and we have the max fworking when V5=0V

For example, in our demo we can calculate a max frequency of ~53KHz (it is V2=2V, and we can assume Vdiode3=0.5V).

The dimming level is set changing potentiometer P<sub>1</sub> value, that makes change the op amp positive reference from 20-30mV to 110-120mV. If we lower R16 we increase the max working frequency and we can lower the dimming level (higher the frequency, lower the current in the lamp arc).

When we try to dim the lamp towards low power range (i.e. <20% electrical arc power) a common effect is the presence of stationary waves along the lamp tube and / or some flickering effects.

A common trick to make these disturbs disappear is to add a small continuos current flow inside the lamp (few mA).

The easiest way to do it is to add a resistor in parallel to the half battery capacitor (C17 in fig. 17/12). For instance we can add 50Kohm (I=200V/50Kohm=4mA) and this is already very effective. Of course the resistor has to be able to sustain the power dissipation caused by the current flow, so it is common to use many resistors connected in parallel.

Just remember, this is only a trick: it helps but it is not enough. It has to be used together with the right frequencies setting that has to be chosen according to the lamp type.

# 6.1 Dimming level and lamp turn on

During the start up sequence the frequency always goes from fmax to fmin, no matter which is the set dimming level. Only after the lamp turn on frequency moves towards higher frequencies. The delay during which f=fmin allows the lamp turn on, but has the drawback of causing a "flash" that can be unpleasant. As the minimum length of this delay depends on the lamp type, it is better to set it as low as possible, finding to best compromise. The easiest way to set this delay is to act on the op amp compensation, i.e. on C9: the higher C9 the longer the delay, the easier the lamp turn on. Values up to 200nF and more are commonly used.

# **AN993 APPLICATION NOTE**

The present note which is for guidance only, aims at providing customers with information regarding their products in order for them to save time. As a result, STMicroelectronics shall not be held liable for any direct, indirect or consequential damages with respect to any claims arising from the content of such a note and/or the use made by customers of the information contained herein in connection with their products.

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics.

All other names are the property of their respective owners

© 2004 STMicroelectronics - All rights reserved

# STMicroelectronics GROUP OF COMPANIES

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States

**57**